Intel търси нови опции за своите бъдещи чипове, включително 3D подреждане на транзистори, за да позволи по-голяма плътност, разширяване на задната мощност и използване на галиев нитрид за по-голямо захранване.

Производителят на чипове Santa Clara показва част от своите изследвания за бъдещ силиций на 69-ата годишна среща на IEEE International Electron Devices Meeting ( IEDM ) в Сан Франциско тази седмица, а El Reg получи предварителен преглед преди събитието.

Intel подробно описа своята технология PowerVia през юни, която премества захранващите линии, които захранват транзисторите, върху обратната страна на силикона – така нареченото обратно захранване – освобождавайки повече място за линиите за свързване, които пренасят сигналите. Това трябва да дебютира на чипове, произведени с производствения възел Intel 20A през първата половина на 2024 г., след което възелът Intel 18A.

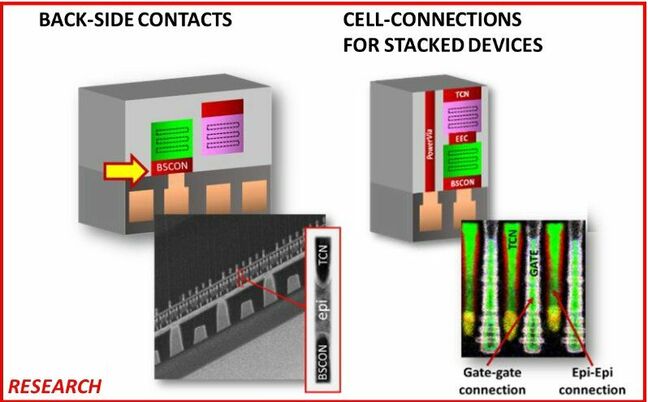

Сега Intel търси мащабиране на задната мощност и разширяване на възможностите си. Една от тези нови функции включва задните контакти, които могат да свързват транзистори от двете страни на устройството за първи път, според сътрудника на Intel за технологично развитие, Мауро Кобрински.

„Сега можем да доставяме захранване директно към устройствата, без да се налага да насочваме захранването около устройствата с PowerVias, и това ни позволява да намалим капацитета на веригата. И с по-нисък капацитет те могат да превключват по-бързо, така че това ни дава по-висока производителност при по-ниска мощност“, твърди Кобрински.

PowerVia също прави възможна друга предложена технология на Intel, подреждане на устройства. Това създава сложна топология за свързване, каза Кобрински, тъй като мощността и сигналите все още трябва да бъдат доставени до горния и долния слой на устройството. PowerVia може да направи това и то по ефективен за зоната начин, когато се използва с вертикални връзки, твърди той.

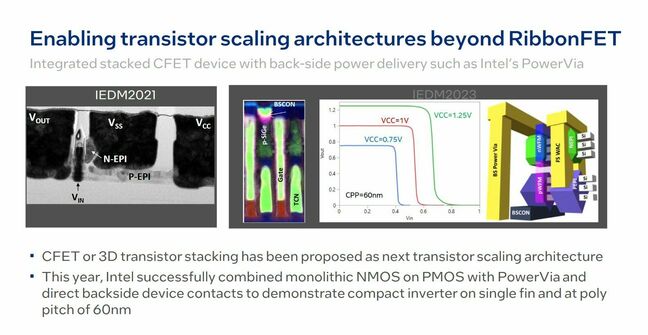

Самото подреждане на устройството се върти около нещо, наречено допълнителен транзистор с полеви ефекти (CFET), предложен като следващия начин за мащабиране на транзистори чрез 3D подреждане на n-тип и p-тип металооксидни полупроводникови устройства едно върху друго. Intel каза, че вижда това като потенциална следваща стъпка след своя RibbonFET, или транзисторен дизайн на gate all-around.

Intel изгради инвертор – много проста схема – използвайки тази технология, при която двата транзистора са подредени вертикално, вместо да са положени един до друг върху силиконовата подложка, което позволява по-големи плътности на компонентите, ако може да бъде мащабирано.

Това е нова технология, която не се използва в момента, според главния инженер на Intel Марко Радосавлевич, поради трудността да се свърже всичко в стека. Но тук идва PowerVia, каза ни той.

„Използваме PowerVia, за да свържем горното устройство надолу към задната страна на пластината, и използваме директните задни контакти, за да свържем долното устройство. Тъй като тези устройства са подредени едно върху друго, няма директен начин да свържем долното устройство към горната страна на пластината, така че трябва да го направим, както току-що беше описано“, каза Радосавлевич.

„Ние сме много развълнувани от перспективите на този тип изследвания, защото ги виждаме като потенциално значително подобрение в гъстотата на устройствата в бъдеще“, добави той.

Инверторът ще бъде демонстриран на IEDM тази седмица, според Intel.

Третата основна тема на Intel за IEDM е използването на галиев нитрид (GaN) в чипове за по-голяма мощност или, по-конкретно, интегрирането на GaN транзистори със силициеви транзистори на една и съща пластина.

GaN устройствата показват печалба почти 20 пъти по-голяма от силициевите устройства като LDMOS, използвани в усилватели на мощност, според главния инженер на Intel Хан Вуи.

(За точност, той всъщност каза, че има стойност, която демонстрира почти 20 пъти повече от силициевите устройства.)

На IEDM Wui е настроен да покаже това, което Intel нарича DrGaN, което е превключвател на захранването, който използва CMOS драйверна верига, комбинирана с GaN транзистори, за да достави мощността, интегрирана в същата матрица.

Чрез интегриране на GaN и силициеви транзистори, Intel каза, че ще може да бъде в крак с плътността на мощността и изискванията за ефективност на бъдещите компютри.

Всички технологии, показани на IEDM, са разработени от Intel’s Components Research Group. Ролята на тази група е по същество да гарантира, че дизайнерите на чипове на компанията имат опции, според директора на Intel за чип Mesoscale Process Development, Пол Фишер.

„Нашата харта е основно да помогне да се гарантира, че технологичното развитие разполага с меню от опции, от които да избира, докато определяме бъдещите технологии за процеси“, каза той.

Тъй като Intel започва да използва задната част на пластината (или матрицата, след като бъде нарязана) за сигнални пътеки, логичната следваща стъпка може да бъде поставянето на някои компоненти там, като двустранна печатна платка. Това ли е нещо, което Intel проучва, попитахме?

Фишер каза, че Intel разглежда различни технологии и така „идеята за поставяне на компоненти и функционалност на задната страна или допълнителни възможности на страната на сигнализирането, това са концепции, които могат да бъдат полезни, и ние продължаваме да разглеждаме концепции като че.“

В крайна сметка всичко се свежда до съвместна оптимизация на системата, каза ни той, подлагайки проектите през стриктна автоматизация на електронния дизайн, инструменти, EDA инструменти и проверявайки дали производителността е достатъчно по-добра, за да оправдае разходите.

Intel също каза, че ще представи първия в света 2D дихалкогениден транзистор с преходен метал (TMD) на IEDM, въпреки че това не беше обсъдено на брифинга за пресата. TMD полупроводниците бяха предложени като бъдеща опция за заместване на силициевите транзистори при физически дължини на портата под 10nm. ®